A 3-D Track-Finding Processor for the CMS Level-1 Muon Trigger

D. Acosta, V. Golovtsov, M. Kan, A. Madorsky, B. Scurlock, H. Stoeck, L. Uvarov, S.M. Wang

## Outline

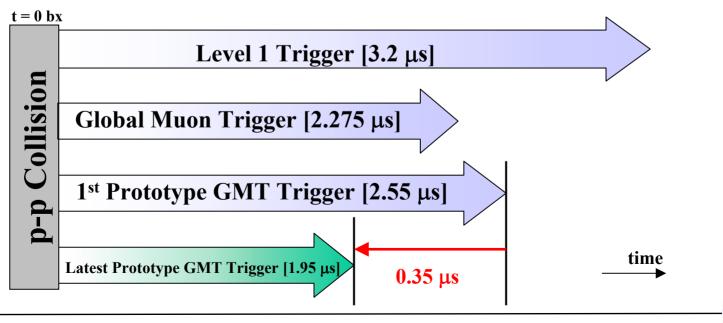

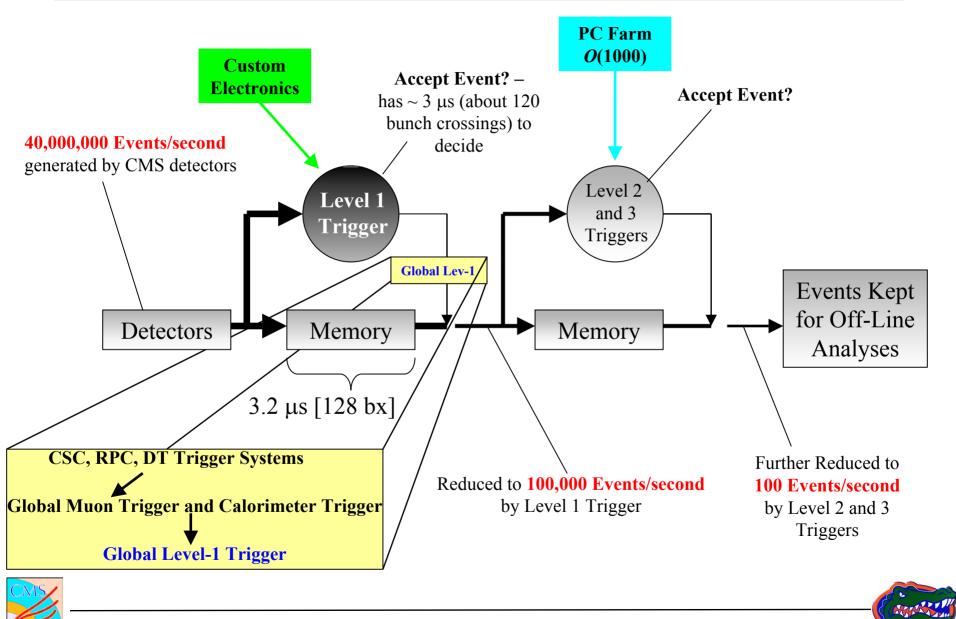

- Level-1 Trigger System

- Track-Finder Electronics

- First Prototype

- Pre-Production Prototype

- Firmware

- Test Results and Plans

# University of Florida

Department of Physics

# The LHC at CERN

- p-p collisions

- $E_{cm} = 14 \text{ TeV}$

- Design Luminosity = 10<sup>34</sup>/cm<sup>2</sup>-s

- Bunch Crossing Frequency = 40 MHz

- Average of 15 pp Collisions/Bunch Crossing

- => Average of 600 Million Proton Interactions per second!!

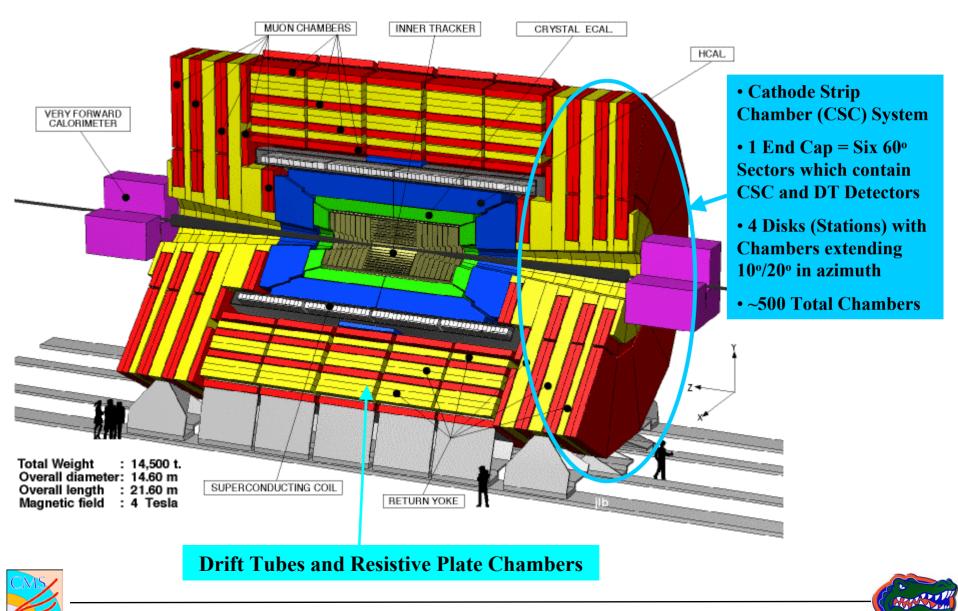

# **CMS** Detectors

## Trigger and Data Acquisition Scheme of CMS

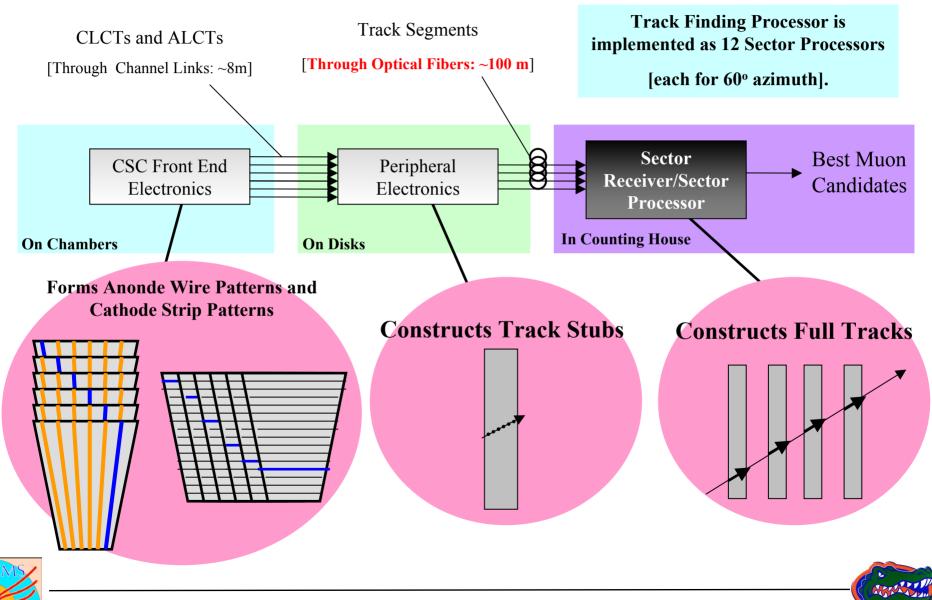

# **CSC Electronics Scheme**

**CSC** Detector

**Electronics**

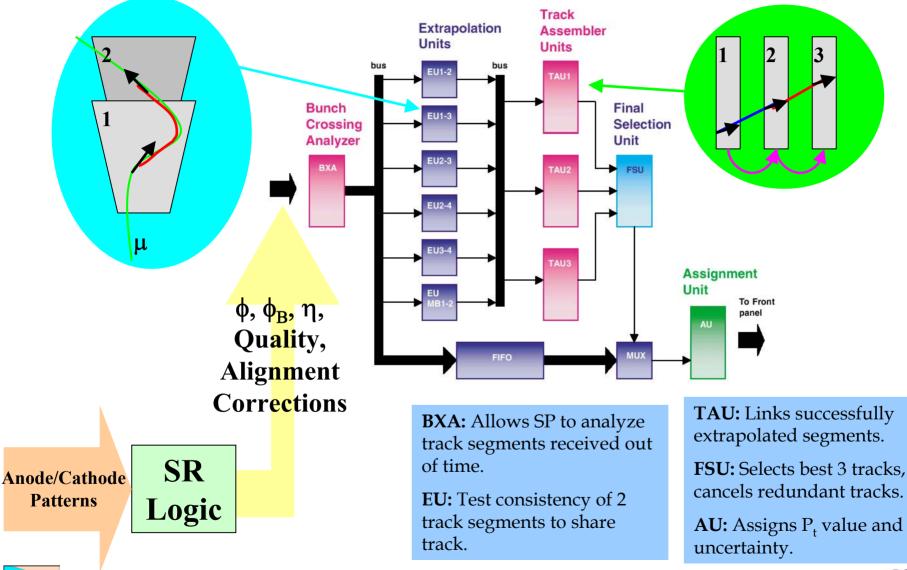

# Basic Design of SR/SP Logic

# **Extrapolation Unit**

## η Road Finder:

-Check if track segment is in allowed trigger region in  $\boldsymbol{\eta}.$

•Check if  $\Delta\eta$  and  $\eta$  bend angle are consistent with a track originating at the collision vertex.

##

-Check if  $\Delta \phi$  is consistent with  $\phi$  bend angle  $\phi_{\rm B}$  measured at each station.

-Check if  $\Delta \phi$  in allowed range for each  $\eta$  window.

### **Quality Assignment Unit:**

•Assigns final quality of extrapolation by looking at output from  $\eta$  and  $\phi$  road finders and the track segment quality.

## Extrapolation Units utilize 3-D information for trackfinding.

CHEP March, 2003. B. Scurlock, University of Florida

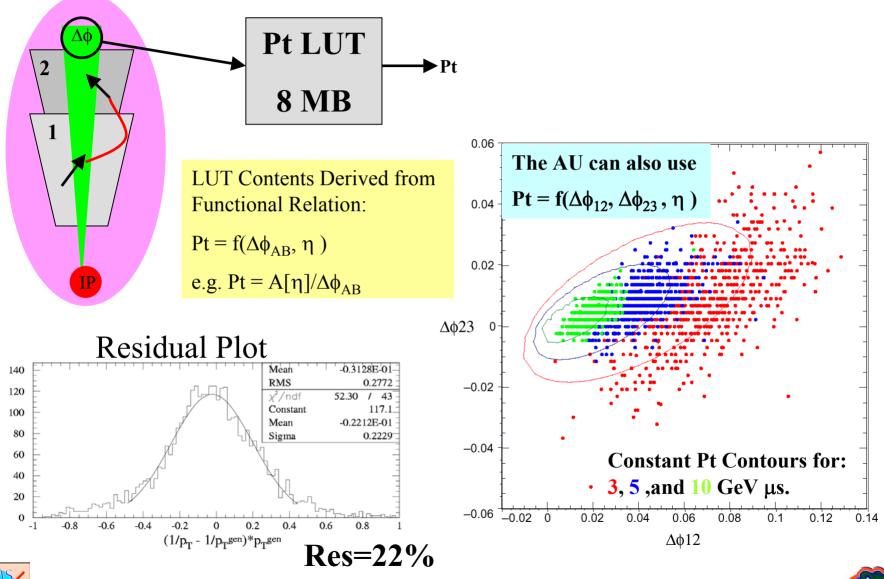

# Pt Assignment Unit

CHEP March, 2003. B. Scurlock, University of Florida

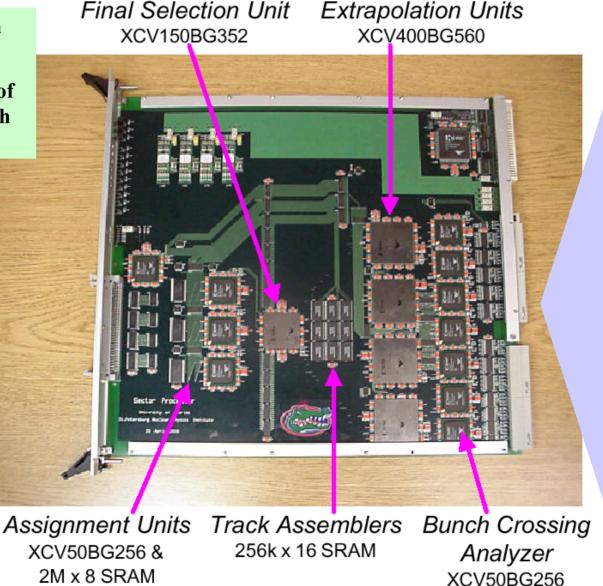

# SP2000 Prototype Design

• Performs 1 Billion Operations/Sec.

• Finishes analyses of data from p-p bunch collision in 375 ns.

12 layers 10K vias 17 FPGAs 12 SRAMs 25 buffers

CMIS/

CHEP March, 2003. B. Scurlock, University of Florida

3GB/s

from 3

Sector

Receiver

Cards

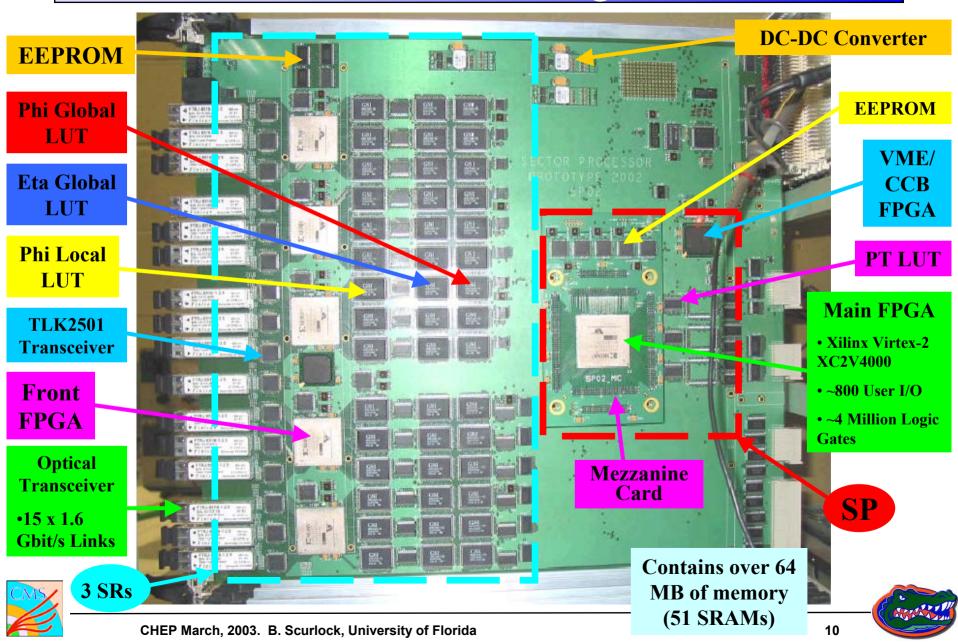

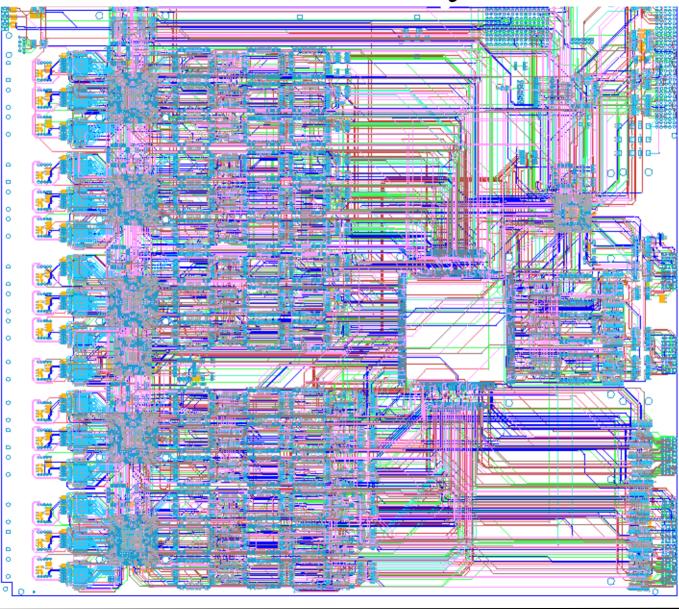

## SP2002: 3 SR's and 1 SP Merged onto 1 Board

# SP2002: 16 Layers

CHEP March, 2003. B. Scurlock, University of Florida

# Verilog++

- SP logic became too complex to rely on schematic-based Firmware.

- A class library has been developed at UF that allows one to write both the simulation code and firmware in C++, and then translate this code into Verilog HDL. Thus, our code serves a dual purpose: when compiled one way we get a simulation, and when we compile the other way we get a Verilog output. This guarantees a bit-for-bit compatible simulation!

- This Verilog code can then be synthesized by our FPGA vendor tools and is used as our SP Firmware. This allows us to verify the SP logic through C++ debugging tools such as MS Visual C++. We can also run this code as a part of the CMS simulation and reconstruction framework - thus allowing us to use usual analysis tools for verification (e.g. ROOT).

- We can thus maintain a line-by-line correspondence between simulation logic and Firmware logic. *Our current Firmware is to be used with a Xilinx Virtex-2 series FPGA*. Example of Verilog shown below:

#### C++:

end

```

always (negedge (vtckp))

begin

If(ConfigReg(0) == 1)

begin

EastWaddr = 0;

WestWaddr = 0;

```

#### **Generated Verilog:**

```

always @(negedge vtckp)

begin

if (ConfigReg[0] == 1)

begin

EastWaddr = 0;

WestWaddr = 0;

end

```

# **Test Results and Future Plans**

- SP2000 was a Success

- **Tests Completed:**

- Downloaded Firmware to FPGAs

- Validated VME Interface

- Validated on-board databus (common to Front FPGA)

**Plans:**

- Test Optical Link Connection to Periperal Electronics.

- Test SR Memories

- Test SP Track-Finding Logic

- Cosmic Ray and Possibly Beam Test

13

# Conclusions

- We have successfully built and tested a prototype trigger which, utilizing 3-D track-finding algorithms, identifies muons in the CSC muon system of CMS, and reports their Pt and angular coordinates to the Global Muon Trigger.

- Receives 3 GB/s of input data and has an expected latency of 250 ns.

- SP2000 successfully tested

- SP2002 has been fabricated. Firmware is being finalized.

- SP2002 Tests well underway.