#### The Track-Finding Processor for the Level-1 Trigger of the CMS Endcap Muon System

D. Acosta, A. Madorsky, B. Scurlock, S.M. Wang University of Florida

A. Atamanchuk, V. Golovtsov, B. Razmyslovich, L. Uvarov

**St. Petersburg Nuclear Physics Institute**

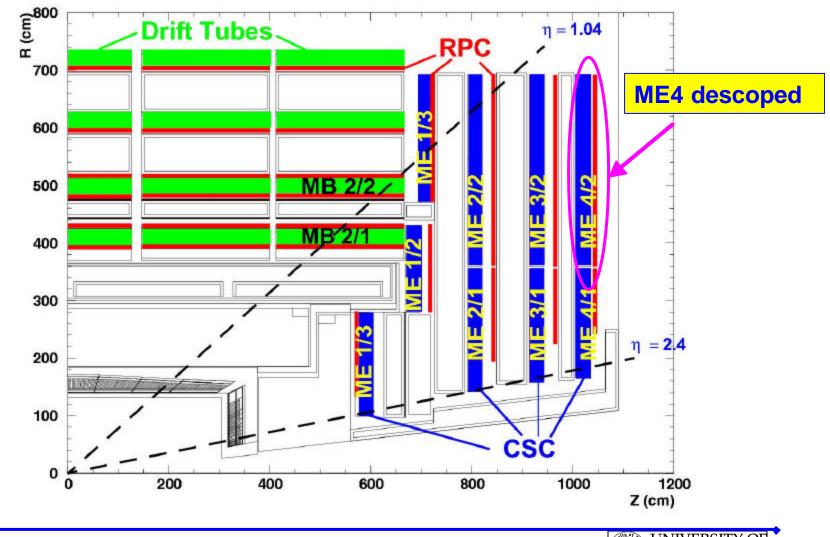

#### **Geometric Coverage**

2

LHC Electronics Workshop 2001

Alex Madorsky

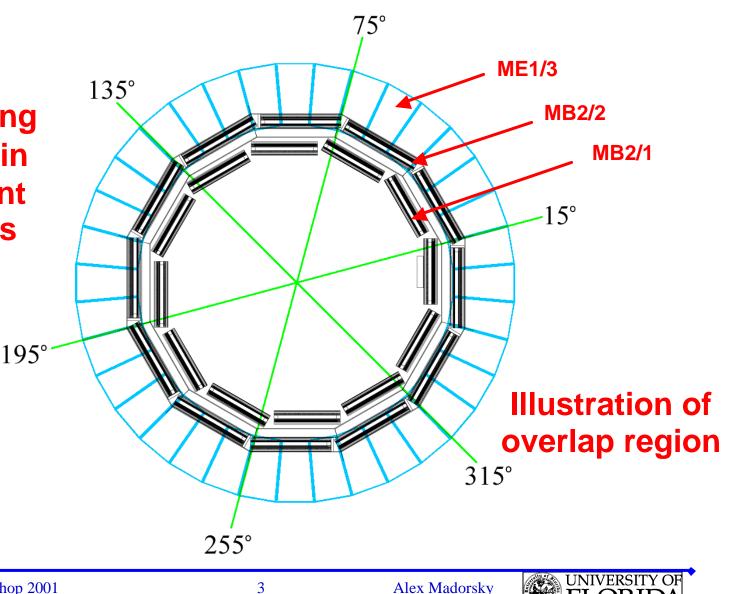

## Trigger Regions in j

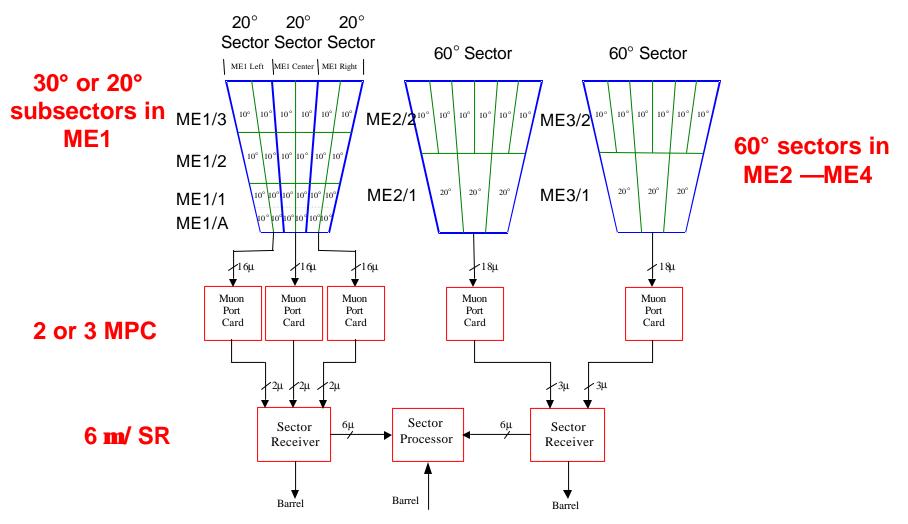

**Track-Finding** performed in independent **60° sectors**

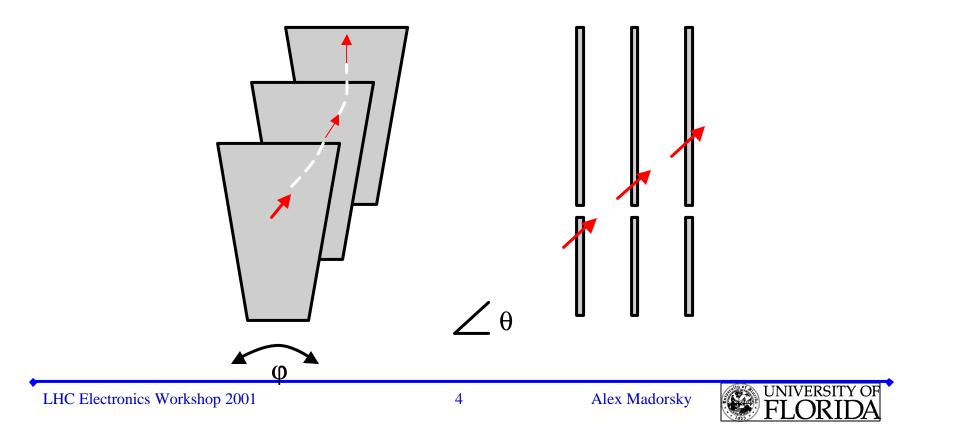

## **Muon Track-Finding**

#### Perform 3D track-finding from trigger primitives Measure $P_T$ , **j**, and **h** Transmit highest $P_T$ candidates to Global L1

### **Sector Partitioning**

5

## **Sector Processor Functionality**

- Identify and measure muons from ~ 600 bits every 25ns (3 GB/s)

- Perform all possible station-to-station extrapolations in parallel

- **Gimultaneously search roads in j and h**

- Assemble 3- and 4-station tracks from 2-station extrapolations

- Cancel redundant short tracks if track is 3 or 4 stations in length

- → Select the three best candidates

- $\rightarrow$  Calculate P<sub>T</sub>, **j**, **h** and send to CSC muon sorter

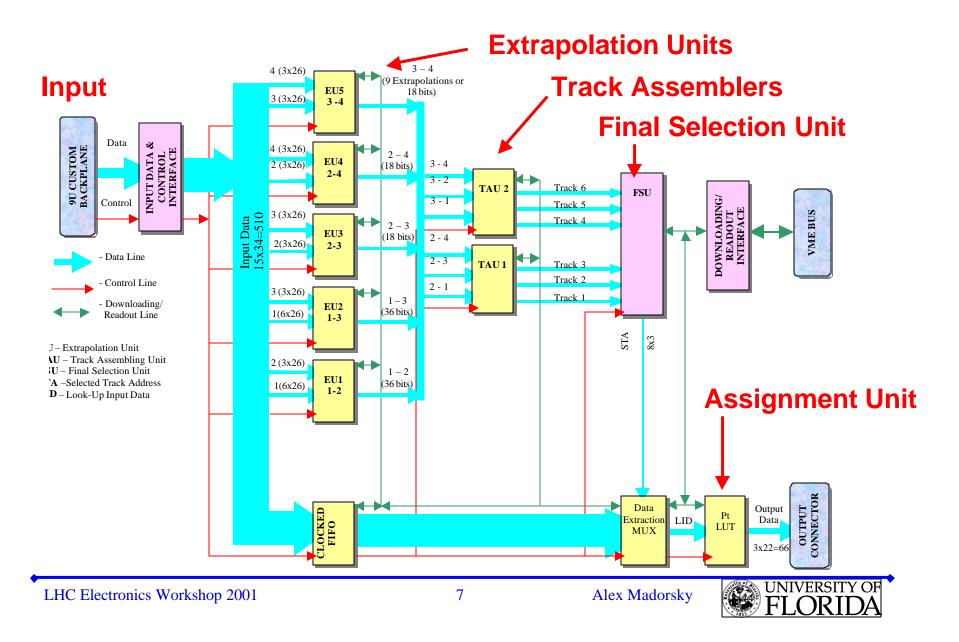

#### **Sector Processor Block Diagram**

#### **Sector Processor Logic**

F

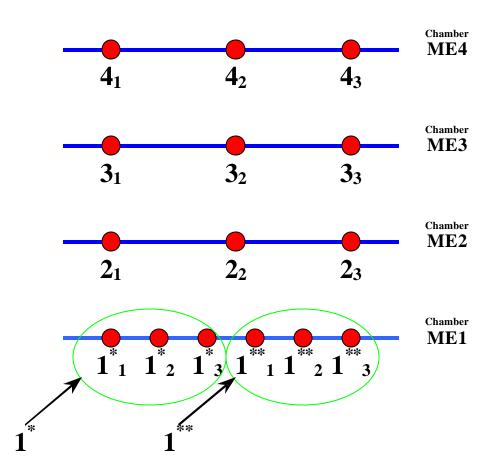

#### Perform all combinations of extrapolations in parallel:

$$\begin{array}{l}

1_{i} \ll 2_{k}, 1_{i} \ll 3_{k}, 2_{i} \ll 3_{k} & 2_{i} \ll 4_{k} \\

4_{k}, 3_{i} \ll 4_{k} \\

But not 1_{i} \ll 4_{k}

\end{array}$$

Track Assembler takes best 2 or 3 extrapolations per reference segment

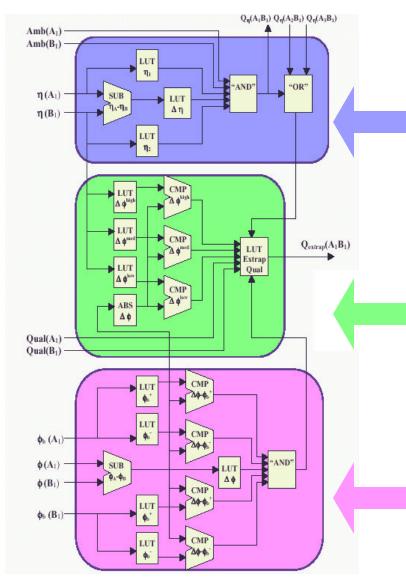

## **Extrapolation Unit**

#### h Road Finder:

-Check if track segment is in allowed trigger region in  $\boldsymbol{\eta}.$

•Check if  $\Delta\eta$  and  $\eta$  bend angle are consistent with a track originating at the collision vertex.

#### **Quality Assignment Unit:**

•Assigns final quality of extrapolation by looking at output from  $\eta$  and  $\phi$  road finders and the track segment quality.

#### **f** Road Finder:

- •Check if  $\Delta \phi$  is consistent with  $\phi$  bend angle  $\phi_b$  measured at each station.

- •Check if  $\Delta \phi$  in allowed range for each  $\eta$  window.

LHC Electronics Workshop 2001

9

## **Track Assembler Unit**

**Functions:**

- Determines if any track segment pairs belong to the same muon

- Combines those segments and assigns a code to denote which muon stations are involved

- Outputs a quality word for the best track for each hit in the key stations (2 and 3)

## **Final Selection Unit**

#### **Functions:**

- Select three best out of nine tracks presented by Track Assemblers

- Cancel redundant tracks (parts of the longer track)

## **Pt Assignment Unit**

# →Calculates P<sub>T</sub>, j, h of the three best muons selected by Final Selection Unit.

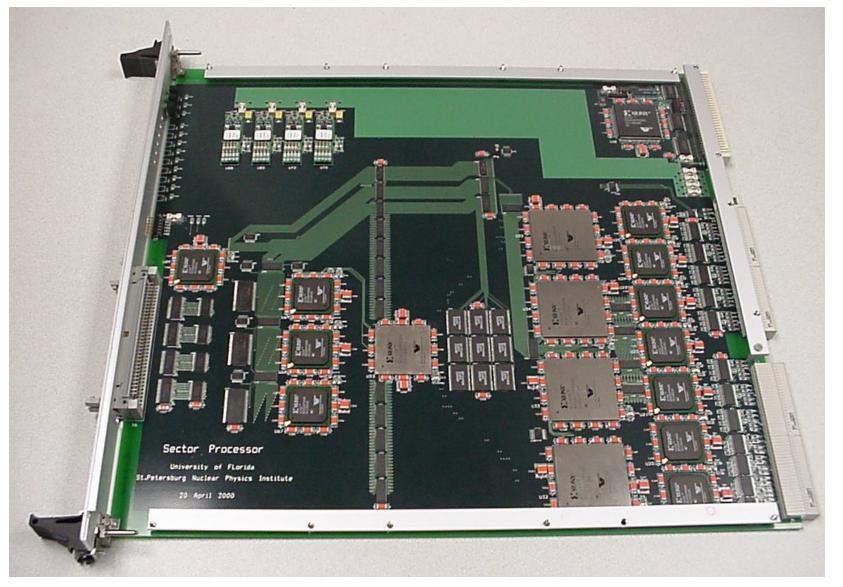

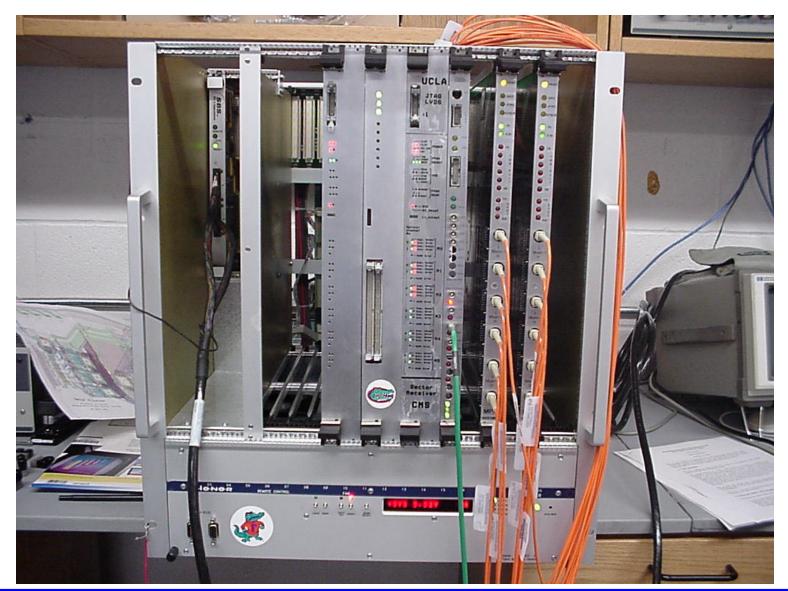

## **First Prototype**

LHC Electronics Workshop 2001

13

### **Custom LVDS Backplane**

#### **Test crate**

15

## **First Prototype Results**

- Track-Finder algorithm implemented in 15 Xilinx Virtex FPGAs, ranging from XCV50 to XCV400

- →One XCV50 for VME interface

- →One XCV50 for output FIFO

- →Latency 15 clocks

- Output compared with C++ model, using simulated input data as well as random numbers, transmitted via custom backplane

- →100% matching demonstrated

### **Test software**

Written:

- Standalone version of the C++ model for Windows

- Module for the comparison of the C++ model with the board's output

- JTAG configuration routine, controlling the fast VME-to-JTAG module of the board

- Lookup configuration routine, used to write and check the on-board lookup memory

- → Board Configuration Database with a Graphical User Interface (GUI), that keeps track of many configuration variants and provides a one-click selection of any one of them. Each variant contains the complete information for FPGA and lookup memory configuration. Can be used for multiple boards.

- To simplify possible porting:

- →All software is written in portable C or C++

- →GUI is written in JAVA

### **Test Software Screenshot**

|                                                                 | add Chip                            | Choose file                 | e remove chip       | Compile file                                                             | Load chip                                                                                                      |                                           |          |          |        |

|-----------------------------------------------------------------|-------------------------------------|-----------------------------|---------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------|----------|--------|

| chip name                                                       | chip type                           | Pos N                       | Node                | file name                                                                |                                                                                                                | X                                         |          |          |        |

| tau_mb_2a                                                       | SP_memory                           | 11 c:                       | sd x_bin/tau_mb_2a_ | Jul291555.bin                                                            |                                                                                                                | ~                                         |          |          |        |

| tau_mb_2b                                                       | SP_memory                           | 11 c:                       | sd x_bin/tau_mb_2b_ | Jul291556.bin                                                            |                                                                                                                | ~                                         |          |          |        |

| au_mb_2c                                                        | SP_memory                           | 11 c:                       | sd x_bin/tau_mb_2c_ | Jul291556.bin                                                            |                                                                                                                | ~                                         |          |          |        |

| au_me_2a                                                        | SP_memory                           | 11 c:                       | sd x_bin/tau_me_2a_ | Jul291557.bin                                                            |                                                                                                                | ~                                         |          |          |        |

| au_me_2b                                                        | SP_memory                           |                             | sd x_bin/tau_me_2b_ |                                                                          |                                                                                                                | ~                                         | 1993     |          |        |

| au_me_2c                                                        | SP_memory                           |                             | sd x_bin/tau_me_2c_ |                                                                          |                                                                                                                | ~                                         |          |          |        |

| au_me_3a                                                        | SP_memory                           |                             | sd x_bin/tau_me_3a_ |                                                                          |                                                                                                                | ~                                         |          |          |        |

| tau_me_3b                                                       | SP_memory                           |                             | sd x_bin/tau_me_3b_ |                                                                          |                                                                                                                | ~                                         |          |          |        |

| tau_me_3c                                                       | SP_memory                           |                             | sd x_bin/tau_me_3c_ | Jul291558.bin                                                            |                                                                                                                | ~                                         | -        |          |        |

| /LoadLookU<br>/tau_me_3b<br>uccessful<br>sponce =0<br>esponse = | _Jul291558.<br>check<br>Ø, time = 1 | LoadLookU<br>bin<br>050msec | ps.exe -b10485760   | -s0x0t<br>-s0x0t<br>tau_<br>tau_<br>tau_<br>tau_<br>tau_<br>tau_<br>tau_ | mb_2c_Jul291556<br>me_2a_Jul291556<br>me_2b_Jul291556<br>me_2c_Jul291556<br>me_3a_Jul291556<br>me_3b_Jul291556 | 7.bin<br>7.bin<br>7.bin<br>8.bin<br>8.bin |          |          |        |

| /LoadLookU<br>/tau_me_3c                                        | ps/Release/<br>_Jul291558.          | LoadLookU<br>bin            | ps.exe -b10485760   | File na                                                                  | me 20 Jul201650                                                                                                | 2a_Jul291                                 | 1557 bin |          | Open   |

| uccessful<br>sponce =0                                          | check                               |                             |                     | =                                                                        |                                                                                                                |                                           |          |          |        |

| esponse =                                                       | 0, time = 9                         | 90msec                      |                     | Files o                                                                  | f type: All Files                                                                                              | (*.*)                                     |          | <b>•</b> | Cancel |

| <sup>7</sup> ull time =                                         | 20650msec                           |                             |                     |                                                                          |                                                                                                                |                                           |          |          |        |

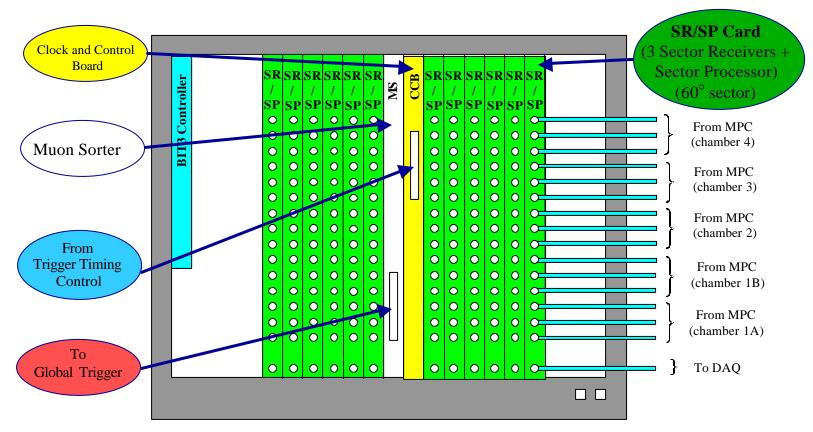

## **Single Crate Solution**

**Track-Finder crate (1.6 Gbits/s optical links)**

- Power consumption: ~ 500W per crate

- 15 optical connections per SR/SP card

- Custom backplane for SR/SPs < > CCB/MS connection

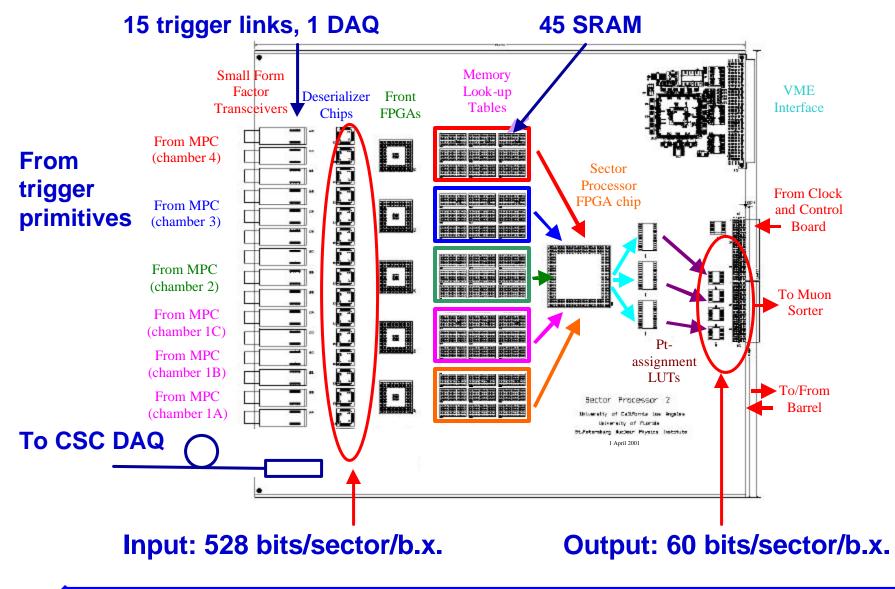

## **Merged SR/SP**

## **Salient Features**

#### **Bi-Directional Optical Links**

- Since we have both transmitters and receivers in the optical connection, this allows the option to send data as well as receive

- Makes testing much easier

- One board sends data to other, or even itself through links

#### SP chip on a mezzanine board

- Decouples board development from FPGA technology

- Makes upgrades easier

#### **DT fan-out on transition board**

- Deliver all possibly needed signals to backplane connector

- Settle transmission technology, connector type, connector count on transition board at a later date

## **SR/SP Inputs**

#### Sent on first frame

| Signal                              | Bits / stub | Bits / 3 stubs<br>(1 MPC) | Bits / 15 stubs<br>(ME1–ME4) | Description                             |           |

|-------------------------------------|-------------|---------------------------|------------------------------|-----------------------------------------|-----------|

| <sup>1</sup> / <sub>2</sub> Strip * | 8           | 24                        | 120                          | <sup>1</sup> / <sub>2</sub> strip label | Reduced   |

| CLCT                                | 4           | 12                        | 75                           | Pattern number without                  | Reduced   |

| pattern *                           |             |                           |                              | 4/6, 5/6, 6/6                           | from 5    |

| L/R bend *                          | 1           | 3                         | 15                           | Sign bit for pattern                    |           |

| Quality *                           | 3           | 9                         | 45                           | Computed by TMB                         |           |

| Wire group                          | 7           | 21                        | 105                          | Wire group label                        |           |

| Accelerator <b>m</b>                | 1           | 3                         | 15                           | Straight wire pattern                   |           |

| CSC i.d.                            | 4           | 12                        | 60                           | Chamber label in                        |           |

|                                     |             |                           |                              | subsector                               |           |

| BXN                                 | 2           | 6                         | 30                           | 2 LSB of BXN                            |           |

| Valid pattern                       | 1           | 3                         | 15                           | Must be set for above                   | Needed    |

|                                     |             |                           |                              | to apply                                | for frame |

| Spare                               | 1           | 3                         | 15                           |                                         |           |

| Total:                              | 32          | 96                        | 480                          | (240 bits at 80 MHz)                    | info      |

#### →DT Track-Finder delivers 2 track stubs each BX via LVDS

| Signal                    | Bits / stub | Bits / 2 stubs<br>(MB1: 60°) | Description                         |

|---------------------------|-------------|------------------------------|-------------------------------------|

| f                         | 12          | 24                           | Azimuth coordinate                  |

| $\mathbf{f}_{\mathrm{b}}$ | 5           | 10                           | <pre>\$ bend angle</pre>            |

| Quality                   | 3           | 6                            | Computed by TMB                     |

| BXN                       | 2           | 4                            | 2 LSB of BXN                        |

| Synch/Calib               | 1           | 2                            | DT Special Mode                     |

| Muon Flag                 | 1           | 2                            | 2 <sup>nd</sup> muon of previous BX |

| Total:                    | 24          | 48                           |                                     |

22

LHC Electronics Workshop 2001

Alex Madorsky

#### **SR/SP Outputs**

#### 6 track stubs are delivered to DT Track-Finder each BX (delivered at 40 MHz to transition board)

| Signal  | Bits / stub | Bits / 2 stubs<br>(ME1: 20°) | Bits / 6 stubs<br>(ME1: 60°) | Bits / 6 stubs<br>@ 80 MHz | Description           |

|---------|-------------|------------------------------|------------------------------|----------------------------|-----------------------|

| f       | 12          | 24                           | 72                           | 36                         | Azimuth coordinate    |

| h       | 1           | 2                            | 6                            | 3                          | DT/CSC<br>region flag |

| Quality | 3           | 6                            | 18                           | 9                          | Computed by TMB       |

| BXN     | _           | 2                            | 6                            | 3                          | 2 LSB of<br>BXN       |

|         | 16          | 34                           | (102)                        | 51                         | Total                 |

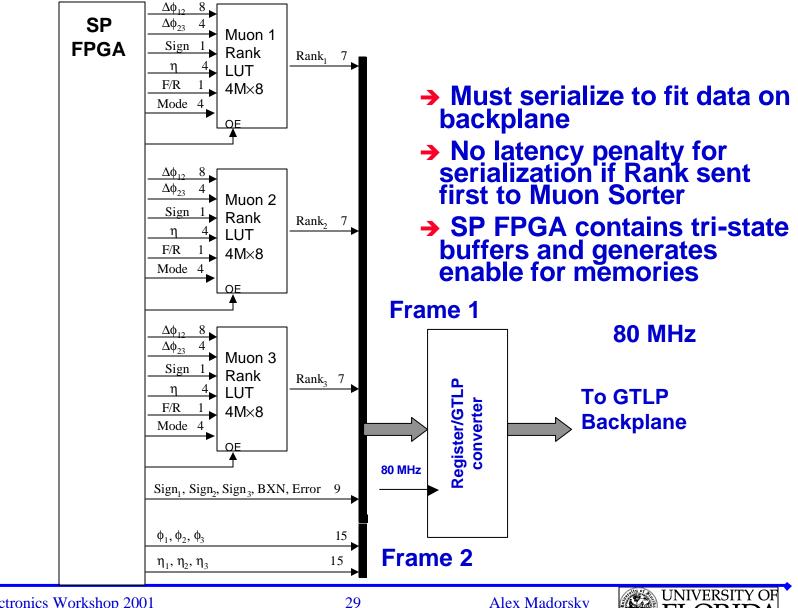

#### → 3 muons per SP are delivered to Muon Sorter via GTLP backplane

|         |          | Signal  | Bits / <b>m</b> | Bits / 3 m<br>(1 SP) | Bits / 36 m<br>(12 SP) | Description                         |

|---------|----------|---------|-----------------|----------------------|------------------------|-------------------------------------|

|         |          | f       | 5               | 15                   | 180                    | Azimuth coordinate                  |

|         |          | h       | 5               | 15                   | 180                    | Pseudorapidity                      |

| Sent on | ſ        | Rank *  | 7               | 21                   | 252                    | 5 bits $p_{\rm T}$ + 2 bits quality |

|         | J        | Sign *  | 1               | 3                    | 36                     |                                     |

| first   | <u>)</u> | BXN *   | —               | 2                    | 24                     | 2 LSB of BXN                        |

| frame   |          | Error * | _               | 1                    | 12                     |                                     |

| nunio   | U        | Spare * | 1               | 3                    | 12                     |                                     |

|         |          | Total:  | 19              | 60                   | 720                    | (360 bits at 80 MHz)                |

### **SR/SP Internal Dataflow**

#### → Data delivered from SR to SP

|      | Signal                | Bits / stub | Bits / 6 stubs<br>(ME1) | Bits / 15 stubs<br>(ME1–ME4) | Description                |

|------|-----------------------|-------------|-------------------------|------------------------------|----------------------------|

|      | f                     | 12          | 72                      | 180                          | Azimuth coordinate         |

|      | <b>f</b> <sub>b</sub> | 5           | 30                      | 75                           | $\phi$ bend angle          |

|      | h                     | 6           | 36                      | 90                           | Pseudorapidity             |

|      | Accelerator <b>m</b>  | 1           | 6                       | 15                           | η bend angle               |

| ME1  | Front/Rear *          | 1           | 6                       | 6                            | ME1 chamber stagger        |

| only | CSC ghost *           | _           | 4                       | 4                            | 2 stubs in same<br>ME1 CSC |

|      | Quality               | 3           | 18                      | 45                           | Computed by TMB            |

|      | Total:                | 28          | 172                     | 415                          | (sent at 80 MHz)           |

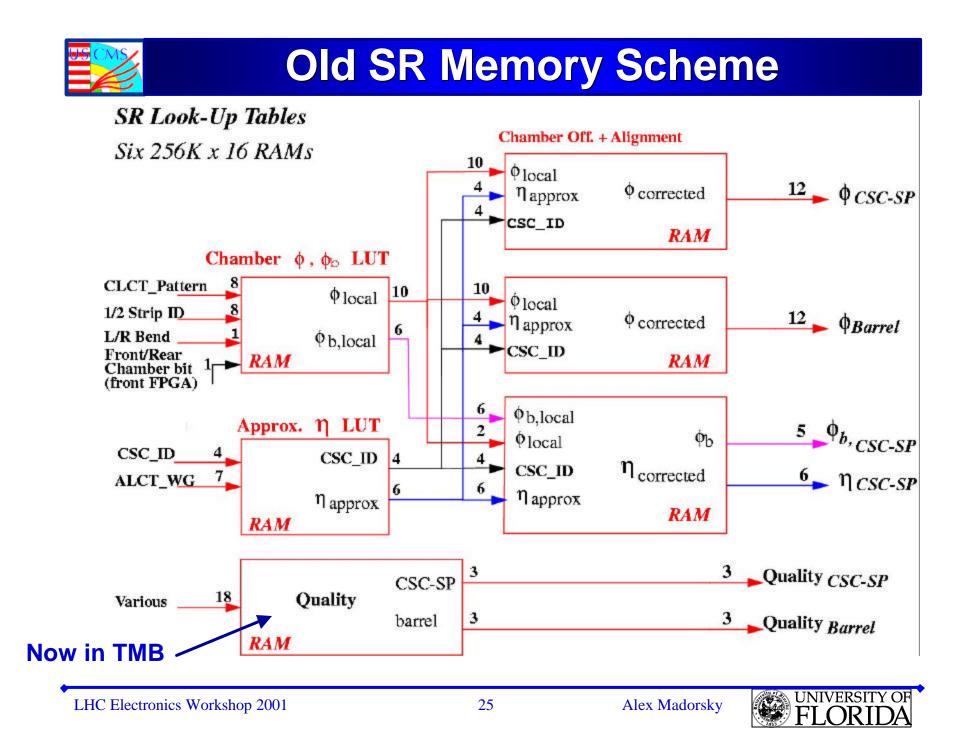

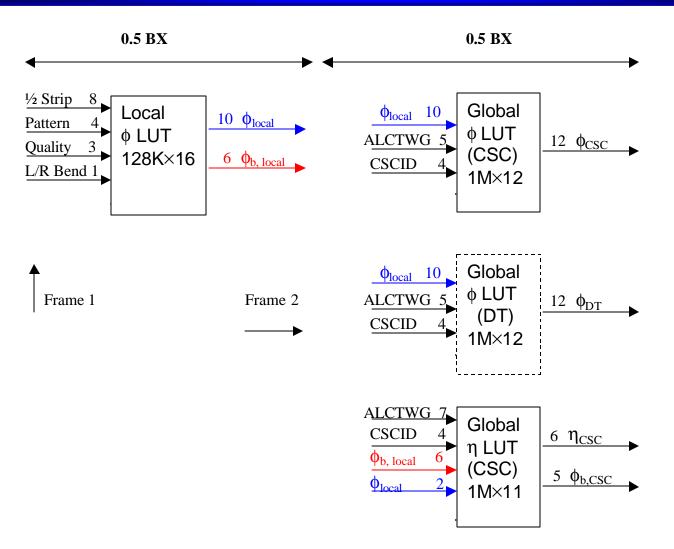

#### **New SR Memory Scheme**

## **Discussion of SR Memory (1)**

#### **Data Frames:**

- → Data arrives off links @ 80 MHz

- The proposed framing scheme implies no latency loss

- First LUT operates on first frame only (but must reduce CLCT pattern label by 1 bit)

- This frame definition must be applied in the TMB where the data is generated and first serialized (i.e. before MPC) to avoid latency penalty

**Memories:**

- → LUT for DT only applies to ME1

- → Chip count is 3 per stub, down from 6 originally

- → Increased memory size to 0.5M (okay for synch. SRAM)

## **Discussion of SR Memory (2)**

#### **One memory set per stub:**

- → 15<sup>-</sup>3 = 45 chips

- → 1 BX latency

- → 415 signals to SP

#### First SR had 36 chips and 1 BX latency

#### **Memory choices:**

- synch SRAM clocked at 160 MHz (tested to this frequency)

- → Flow Through SRAM clocked at 80 MHz

### **Pt Assignment Memory Scheme**

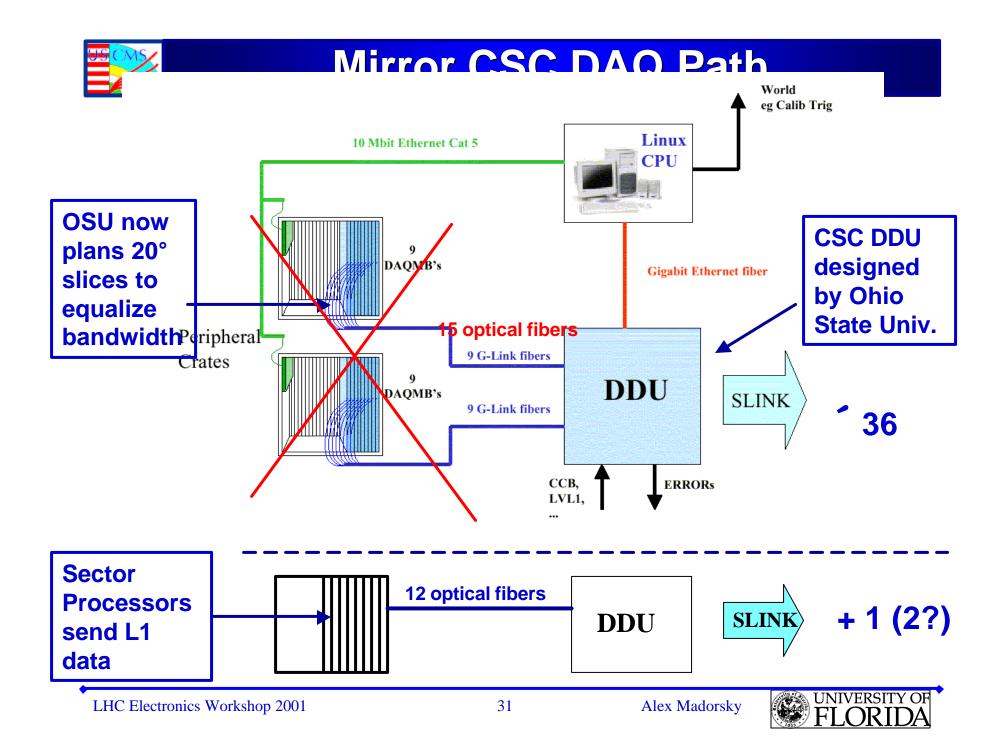

### **CSC TF DAQ Plans**

Send input of SR and output of SP to DAQ stream for diagnostics

Track-Finder DAQ acts as additional DDU for EMU system

- Plan to use existing DDU design by OSU

- **OSU** has decided to use T.I. Chip for serialization

- **12 SP fiber connections fits well into 15 planned for DDU**

LHC Electronics Workshop 2001

UNIVERSITY OF

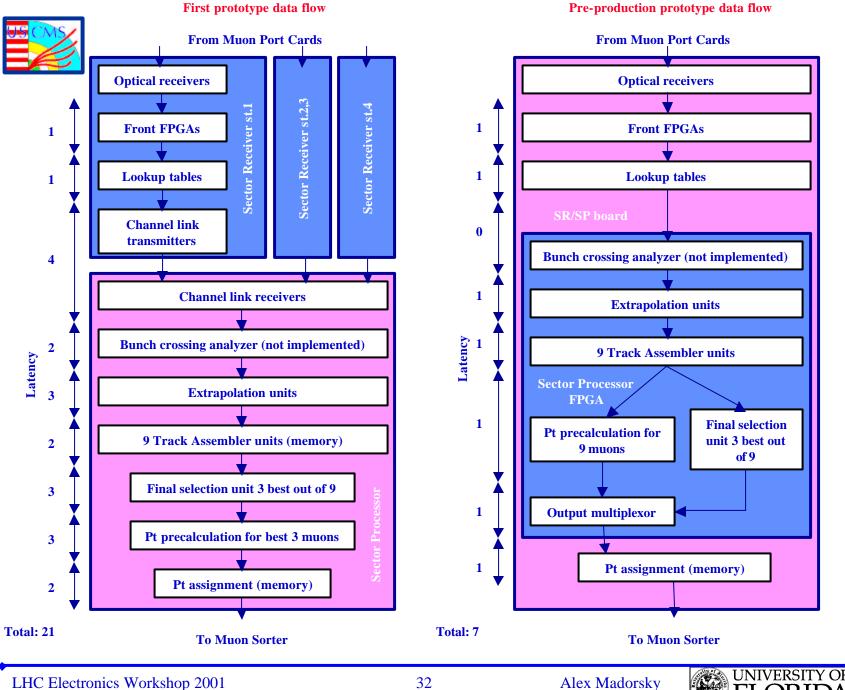

## **Pre-Production Prototype**

Done:

- →SP algorithm is rewritten in Verilog HDL

- →New C++ model line-by-line corresponds to Verilog HDL code

- If Verilog HDL code is written properly, C++ conversion is very simple and straightforward

- →New C++ model matches the functionality of the original C++ model

- →SP-Verilog has been extensively simulated and is working in exact correspondence to functionality of the first prototype and both C++ models

- Simulated latency for Sector Processor Algorithm: 5 clocks (15 in the first prototype)

- →Board development underway

Plans:

- →Replacing the original C++ model with the new one in ORCA

- Adding new features into the SP-Verilog code and C++ model simultaneously, keeping them in strict line-by-line correspondence

## **SP Algorithm Modifications**

- Extrapolation and Final Selection units are reworked, and now each of them is completed in only one clock.

- → The Track Assembler Units in the first prototype were implemented as external lookup tables (static memory). For the second prototype, they are implemented as FPGA logic. This saved I/O pins on the FPGA and one clock of the latency.

- The preliminary calculations for the PT assignment are done in parallel with final selection for all 9 muons, so when three best out of nine muons are selected, the pre-calculated values are immediately sent to the external PT assignment lookup tables.

### Acknowledgements

This work was supported by grants from the US Department of Energy.

We also would like to acknowledge the efforts of R. Cousins, J. Hauser, J. Mumford, V. Sedov, B. Tannenbaum, who developed the first Sector Receiver prototype, and the efforts of M. Matveev and P. Padley, who developed the Muon Port Card and Clock and Control Board, which were used in the tests.

35