CSC Track-Finder HW/SW Update

# Bobby Scurlock, UF Darin Acosta, UF Alex Madorski, PNPI Lev Uvarov, PNPI Victor Golovtsov, PNPI

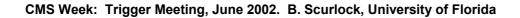

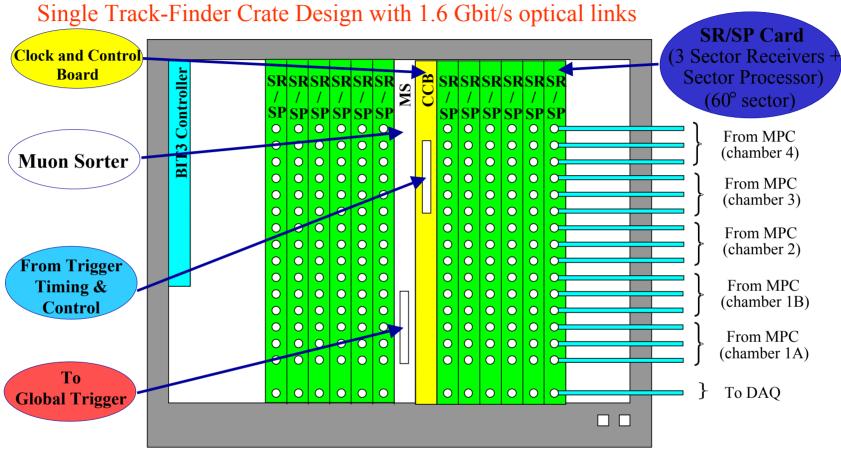

#### New Track-Finder Crate Design

- Reduces  $\overline{SR/SP}$  processing time from 21 bx (old design) to 7 bx

- Crate Power Consumption  $\sim 1000 \text{ W}$

- 16 Optical connections per SR/SP card

- − Custom Backplane for SR/SP ⇔ CCB and MS connection

# **DT-CSC** Interface Specified

- DT/CSC transition board pinout specified

- Connector pinout to DT/CSC transition board defined

- Would like to specify DT/CSC cable pinout

- CMS IN 2002/040 released

| Signal  | Bits/stub | Bits/3 stubs | Bits/6 stubs | Description        |

|---------|-----------|--------------|--------------|--------------------|

| $\phi$  | 12        | 36           | 72           | Azimuth coordinate |

| $\eta$  | 1         | 3            | 6            | DT/CSC region flag |

| Quality | 3         | 9            | 18           | stub quality       |

| BXN     | —         | 2            | 4            | 2 LSB of BXN       |

| BC0     | _         | 1            | 2            | bunch crossing 0   |

| Clock   | —         | 1            | 2            | clock for data     |

| Total:  | 16        | 52           | 104          |                    |

#### **DT TF→ CSC TF**

| Signal    | Bits/stub | Bits/2 stubs | Description             |

|-----------|-----------|--------------|-------------------------|

| $\phi$    | 12        | 24           | Azimuth coordinate      |

| $\phi_b$  | 5         | 10           | $\phi$ bend angle       |

| Quality   | 3         | 6            | stub quality            |

| Muon Flag | 1         | 2            | 2nd muon of previous BX |

| BXN       | 2         | 4            | 2 LSB of BXN            |

| BC0       | 1         | 2            | bunch crossing 0        |

| Calib     | 1         | 2            | data not valid          |

| Clock     | 1         | 2            | clock for data          |

| Total:    | 26        | 52           |                         |

$\mathbf{CSC} \mathbf{TF} \rightarrow \mathbf{DT} \mathbf{TF}$

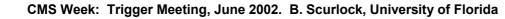

#### SR/SP 2002 Board Layout

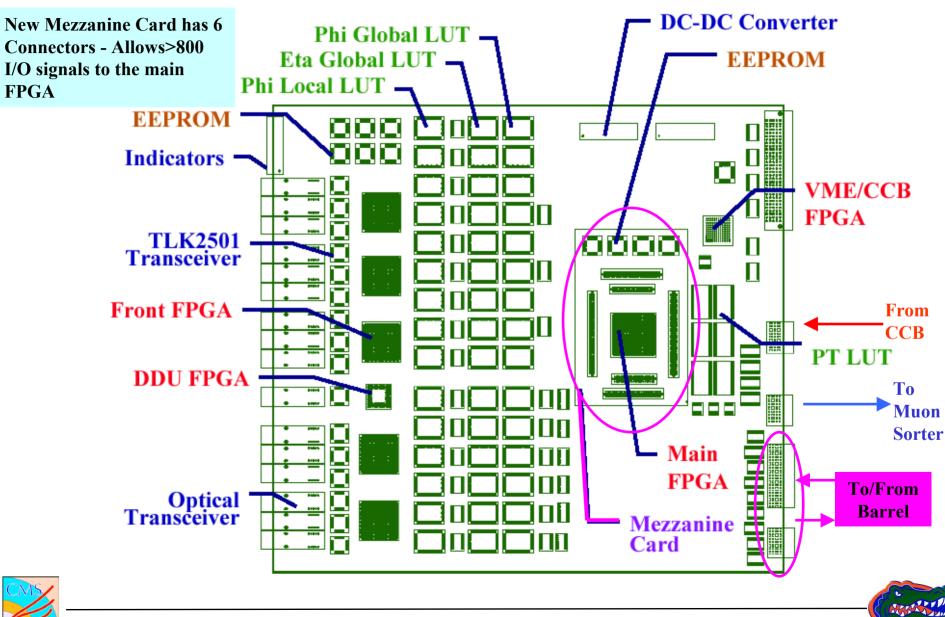

•SR now has 3 memories rather than 6 per stub [total of 45 per board]. Need to define their contents. LUTs are created in ORCA, but have yet to be tested.

•>64 MB per board ⇒ Need high VME bandwidth, broadcast capability to identical chips, and crate broadcast capability to SPs

# SR/SP 2002 Design Status

- Schematics Complete:

- Sector Receiver Front FPGAs (5 total)

- Choice: XC2V1000-FF896C with 432 user I/Os

- Sector Processor Main FPGA

- Choice: XC2V4000-FF1152C with 824 user I/Os

- Placed on mezzanine card (design started)

- Firmware written in "Verilog++", validated by simulation

- VME & control interface FPGA

- Choice: XC2V250-FG456C with 200 user I/Os

- DAQ Interface FPGA

- Choice: XC2V250-FG256C with 172 user I/Os

- SRAM:

- 51 SRAM chips (>64MB) for Look-up functionality

- May require BGA packages to allow more space for routing

- Layout to commence soon

– Board will be dense! (Merger of 4 boards, but I/O ~same)

7

# Software Update

- Verilog++ SP model implemented and LUTs generated in ORCA.

- Also need to add Bunch Crossing Analyzer and Ghost Busting [background reduction] to Verilog++ model.

- Phi and Eta SR LUT Contents Have Been Specified in ORCA. [Thank You Slava Valouev!]

- Work underway to attach track-stub data to tracks in Verilog++ model and in DAQ (this will be useful for L2 Trigger).

### Software Update

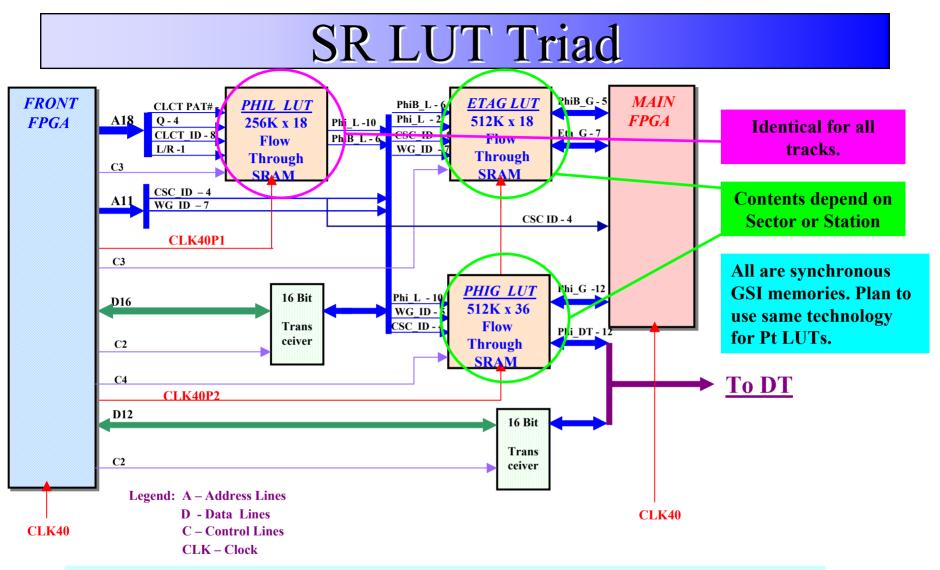

Currently examining alternative bend patterns in CLCT Processor to improve φ resolution and Pt assignment.

• First attempt will be using patterns from CMSIM100 ⇒ Bend value based only on the number of strips extended. For example:

CMS Week: Trigger Meeting, June 2002. B. Scurlock, University of Florida

#### Test Software Update

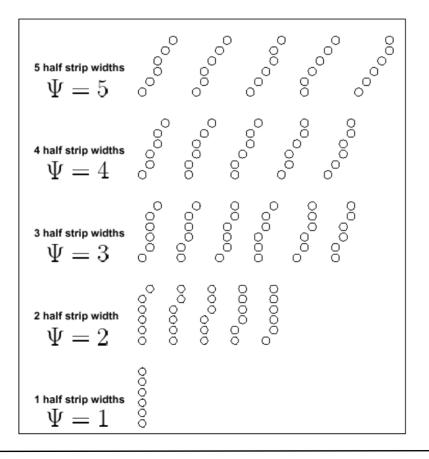

We have started working on integrating software written for the 2000 TF crate tests into the XDAQ environment.

- 🗆 × JAVA GUI and add Chir Choose file **Compile file** Load chip configuration chip name chip type Pos Mode file name X tau mb 2a SP memory 11 csd x bin/tau mb 2a Jul291555.bin database tau\_mb\_2b SP\_memory 11 csd x\_bin/tau\_mb\_2b\_Jul291556.bin SP\_memory 11 x bin/tau mb 2c Jul291556.bin au mb 2 csd tau\_me\_2a SP\_memory 11 csd x\_bin/tau\_me\_2a\_Jul291557.bin SP memory 11 csd x\_bin/tau\_me\_2b\_Jul291557.bin tau me 2b SP\_memory 11 x\_bin/tau\_me\_2c\_Jul291557.bin au me 2 csd SP\_memory 11 csd x bin/tau me 3a Jul291558.bin au me 3a SP\_memory csd x\_bin/tau\_me\_3b\_Jul291558.bin 11 tau me 3b 11 csd x\_bin/tau\_me\_3c\_Jul291558.bin au\_me\_3 SP memory St Oper - 🖬 🏦 🗂 👯 🗄 x bin Look in: 🗉 🗆 🛍 🛃 🖴 A Auto uccessful check tau mb 2b Jul291556.bin snonce = tau mb 2c Jul291556.bin response = 0, time = 1040msec tau\_me\_2a\_Jul291557.bir ./LoadLookUps/Release/LoadLookUps.exe -b10485760 -s0x08 n/tau me 3b Jul291558.bin Thau me 2b Jul291557.bir tau\_me\_2c\_Jul291557.bin successful check snonce =0 htau me 3a Jul291558.bin response = 0, time = 1050msec Thau me 3b Jul291558.bin ./LoadLookUps/Release/LoadLookUps.exe -b10485760 -s0x08 n/tau\_ne\_3c\_Jul291558.bin 2e 101201650 his tau\_me\_2a\_Jul291557.bin File name: Open successful check esponce =0 Files of type: All Files (\*.\*) Cancel response = 0, time = 990msec Full time = 20650msec Command-line programs to load FPGAs and LUTs 🏦 Start 🛛 💁 C:\agatam\0... 🔛 Programmer's ... 🏙 LoadLookUps 🛛 💆 Load Chips 🔹 Exploring - My... 🕅 📉 🚫 🎔 🗹 🔄 🖬 🖬 🏉 🍏 🗳 4:35 PM

Screen shot of

the Hardware

configuration

GUI.

# Schedule

• November 2002: expect to finish the SP protoype. Will conduct single board tests

- MPC $\rightarrow$ SR/SP tests will continue through to 4/30/03.

- 5/1/03 to 9/30/03: Plan chain tests with CSC chambers and front-end electronics using cosmic rays and test beam.

- Also plan to do DT↔CSC tests sometime after May 1 2003.

#### Conclusions

- CSC TF Backplane Specified

- **DT-CSC Interface Specified**

- SR/SP Schematics Complete

- SR/SP Layout Started

- SR LUT Generation Completed in ORCA

- More Additions Scheduled for Verilog++ SP Model

- Work on  $\phi_b$  Definition in Progress