## **Conceptual Design for SR/SP**

### **Topics:**

- Board Layout

- Bit counts and data serialization

- Memory architecture (PNPI)

- → SP to Verilog Translation (Madorsky)

- DDU plans

1

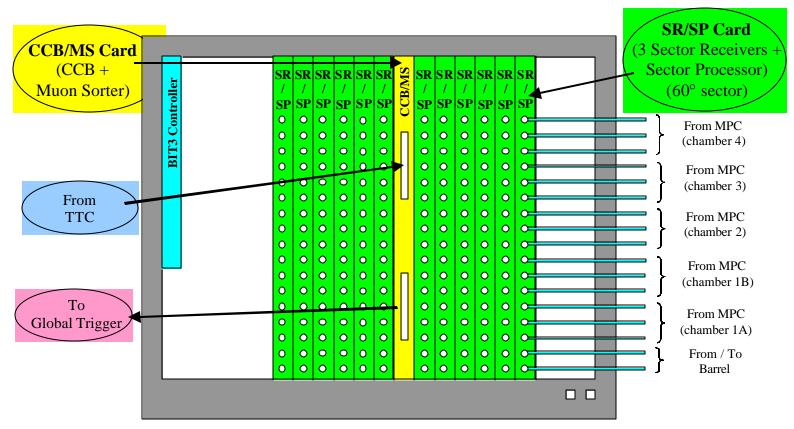

## **Possible Single Crate Solution**

#### **Track-Finder crate (1.6 Gbits/s optical links)**

- Total latency: ~ 20Bx (from input of SR/SP card to output of CCB/MS card)

- Power consumption: ~ 500W per crate

- 15 ptical connections per SR/SP card

- Custom backplane for SR/SPs <> CCB/MS connection

## **Merged SR/SP**

3

USCMS Trigger Meeting, August 2001

## **Salient Features**

### **Bi-Directional Optical Links**

- →Since we have both transmitters and receivers in the optical connection, this allows the option to send data as well as receive

- Makes testing much easier

- One board sends data to other, or even itself through links

### SR memory set for each muon stub

- No muon multiplexing means shortest latency

- SP chip on a mezzanine board

- Decouples board development from FPGA technology

- → Makes upgrades easier

- **DT fan-out on transition board**

- Deliver all possibly needed signals to backplane connector

- Settle transmission technology, connector type, connector count on transition board at a later date

USCMS Trigger Meeting, August 2001

## **SR/SP Inputs**

#### Sent on first frame

| Signal                              | Bits / stub | Bits / 3 stubs<br>(1 MPC) | Bits / 15 stubs<br>(ME1–ME4) | Description                             |           |

|-------------------------------------|-------------|---------------------------|------------------------------|-----------------------------------------|-----------|

| <sup>1</sup> / <sub>2</sub> Strip * | 8           | 24                        | 120                          | <sup>1</sup> / <sub>2</sub> strip label | Deduced   |

| CLCT                                | 4           | 12                        | 75                           | Pattern number without                  | Reduced   |

| pattern *                           |             |                           |                              | 4/6, 5/6, 6/6                           | from 5    |

| L/R bend *                          | 1           | 3                         | 15                           | Sign bit for pattern                    |           |

| Quality *                           | 3           | 9                         | 45                           | Computed by TMB                         |           |

| Wire group                          | 7           | 21                        | 105                          | Wire group label                        |           |

| Accelerator <b>m</b>                | 1           | 3                         | 15                           | Straight wire pattern                   |           |

| CSC i.d.                            | 4           | 12                        | 60                           | Chamber label in subsector              |           |

| BXN                                 | 2           | 6                         | 30                           | 2 LSB of BXN                            |           |

| Valid pattern                       | 1           | 3                         | 15                           | Must be set for above to apply          | Needed    |

| Spare                               | 1           | 3                         | 15                           |                                         | for frame |

| Total:                              | 32          | 96                        | 480                          | (240 bits at 80 MHz)                    | info      |

#### →DT Track-Finder delivers 2 track stubs each BX via LVDS

| Signal                    | Bits / stub | Bits / 2 stubs | Description                         |

|---------------------------|-------------|----------------|-------------------------------------|

|                           |             | (MB1: 60°)     |                                     |

| f                         | 12          | 24             | Azimuth coordinate                  |

| $\mathbf{f}_{\mathrm{b}}$ | 5           | 10             | <pre>\$ bend angle</pre>            |

| Quality                   | 3           | 6              | Computed by TMB                     |

| BXN                       | 2           | 4              | 2 LSB of BXN                        |

| Synch/Calib               | 1           | 2              | DT Special Mode                     |

| Muon Flag                 | 1           | 2              | 2 <sup>nd</sup> muon of previous BX |

| Total:                    | 24          | 48             |                                     |

5

USCMS Trigger Meeting, August 2001

**Darin Acosta**

### **SR/SP Outputs**

#### → 6 track stubs are delivered to DT Track-Finder each BX (delivered at 40 MHz to transition board)

| Signal  | Bits / stub | Bits / 2 stubs<br>(ME1: 20°) | Bits / 6 stubs<br>(ME1: 60°) | Bits / 6 stubs<br>@ 80 MHz | Description           |

|---------|-------------|------------------------------|------------------------------|----------------------------|-----------------------|

| f       | 12          | 24                           | 72                           | 36                         | Azimuth coordinate    |

| h       | 1           | 2                            | 6                            | 3                          | DT/CSC<br>region flag |

| Quality | 3           | 6                            | 18                           | 9                          | Computed by TMB       |

| BXN     | _           | 2                            | 6                            | 3                          | 2 LSB of<br>BXN       |

|         | 16          | 34                           | (102)                        | 51                         | Total                 |

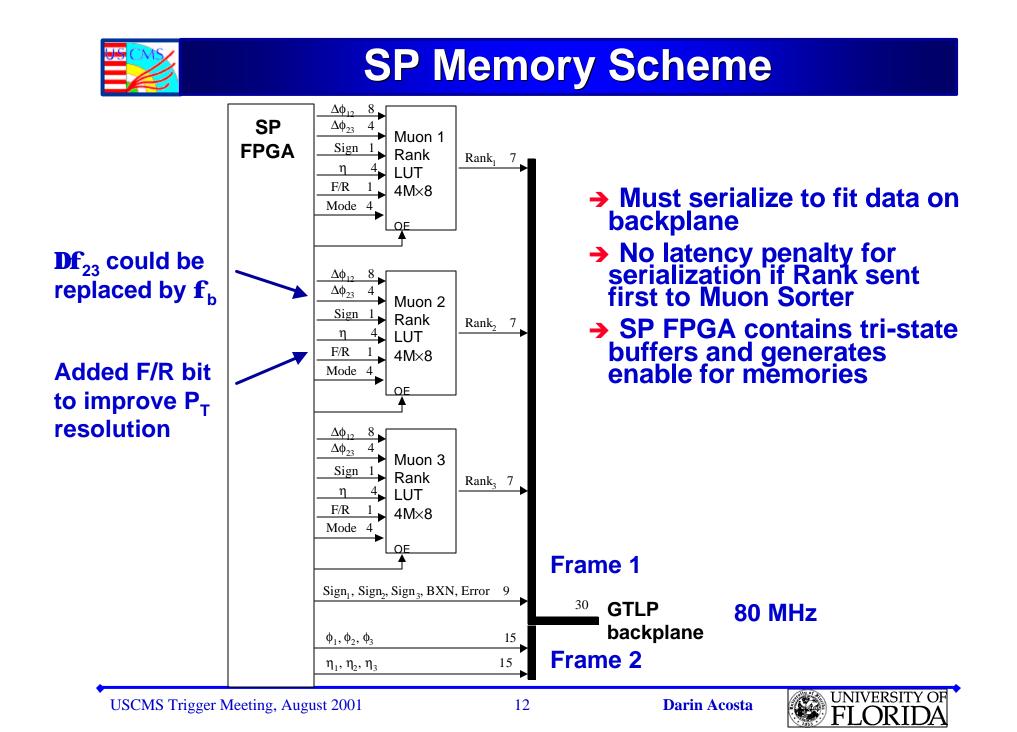

#### → 3 muons per SP are delivered to Muon Sorter via GTLP backplane

|         |          | Signal  | Bits / <b>m</b> | Bits / 3 m<br>(1 SP) | Bits / 36 m<br>(12 SP) | Description                         |

|---------|----------|---------|-----------------|----------------------|------------------------|-------------------------------------|

|         |          | f       | 5               | 15                   | 180                    | Azimuth coordinate                  |

|         |          | h       | 5               | 15                   | 180                    | Pseudorapidity                      |

| Sent on | ſ        | Rank *  | 7               | 21                   | 252                    | 5 bits $p_{\rm T}$ + 2 bits quality |

|         | J        | Sign *  | 1               | 3                    | 36                     |                                     |

| first   | <u>)</u> | BXN *   | —               | 2                    | 24                     | 2 LSB of BXN                        |

| frame   |          | Error * | —               | 1                    | 12                     |                                     |

| iramo   | L.       | Spare * | 1               | 3                    | 12                     |                                     |

|         |          | Total:  | 19              | 60                   | 720                    | (360 bits at 80 MHz)                |

**Darin Acosta**

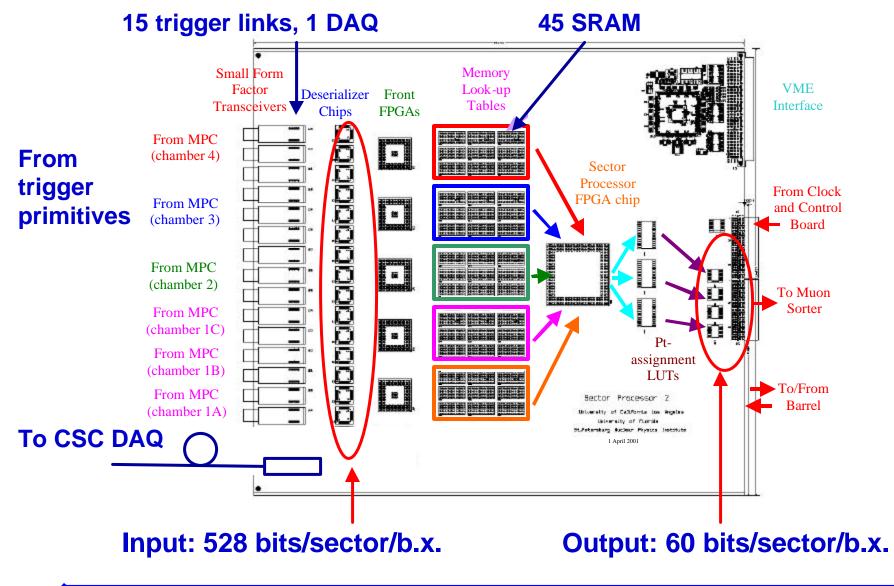

## **SR/SP Internal Dataflow**

#### → Data delivered from SR to SP

|       | Signal                | Bits / stub | Bits / 6 stubs<br>(ME1) | Bits / 15 stubs<br>(ME1–ME4) | Description                |

|-------|-----------------------|-------------|-------------------------|------------------------------|----------------------------|

|       | f                     | 12          | 72                      | 180                          | Azimuth coordinate         |

|       | <b>f</b> <sub>b</sub> | 5           | 30                      | 75                           | $\phi$ bend angle          |

| ME1 { | h                     | 6           | 36                      | 90                           | Pseudorapidity             |

|       | Accelerator <b>m</b>  | 1           | 6                       | 15                           | η bend angle               |

|       | Front/Rear *          | 1           | 6                       | 6                            | ME1 chamber stagger        |

|       | CSC ghost *           | _           | 4                       | 4                            | 2 stubs in same<br>ME1 CSC |

|       | Quality               | 3           | 18                      | 45                           | Computed by TMB            |

|       | Total:                | 28          | 172                     | 415                          | (sent at 80 MHz)           |

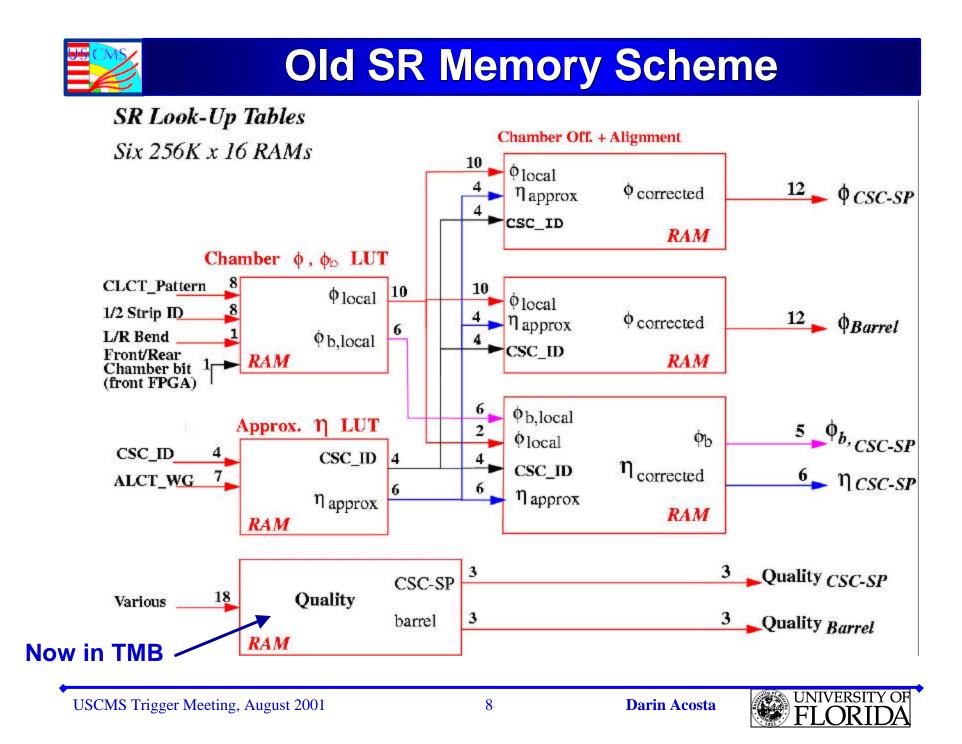

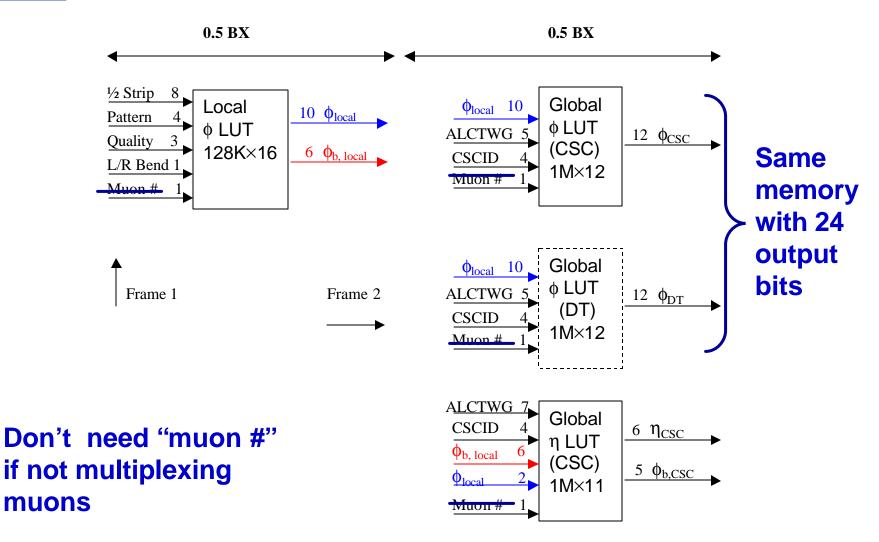

### **New SR Memory Scheme**

USCMS Trigger Meeting, August 2001

**Darin Acosta**

9

## **Discussion of SR Memory (1)**

### **Data Frames:**

- → Data arrives off links @ 80 MHz

- The proposed framing scheme implies no latency loss

- First LUT operates on first frame only (but must reduce CLCT pattern label by 1 bit)

- This frame definition must be applied in the TMB where the data is generated and first serialized (i.e. before MPC) to avoid latency penalty

### **Memories:**

- → LUT for DT only applies to ME1

- → Chip count is 3 per stub, down from 6 originally

- → Increased memory size to 0.5M (okay for synch. SRAM)

- "Muon #" only applies if more than one stub in a BX is sent through same memory

## **Discussion of SR Memory (2)**

### **One memory set per stub:**

- → 15<sup>-</sup>3 = 45 chips

- → 1 BX latency

- → 415 signals to SP

### First SR had 36 chips and 1 BX latency

### **Memory choices:**

- synch SRAM clocked at 160 MHz (tested to this frequency)

- → Flow Through SRAM clocked at 80 MHz (see PNPI)

## **SP to Verilog translation**

What we said last time:

# Will overhaul some of the SP software/firmware to facilitate changes to both

- → Have SW algorithms match Verilog/Schematics better

- → Have SW read same HW LUTs (it already generates them)

### Plan to test next SP design even before construction!

- Add utilities to write ORCA data into Xilinx simulator format and to compare simulator output to ORCA

- → Gives us a head start on validating logic design

- Will allow us to focus on HW debugging rather than SW debugging when testing the next prototype

### This is now done! Latency: 12 ® 5 BX (See Madorsky)

USCMS Trigger Meeting, August 2001

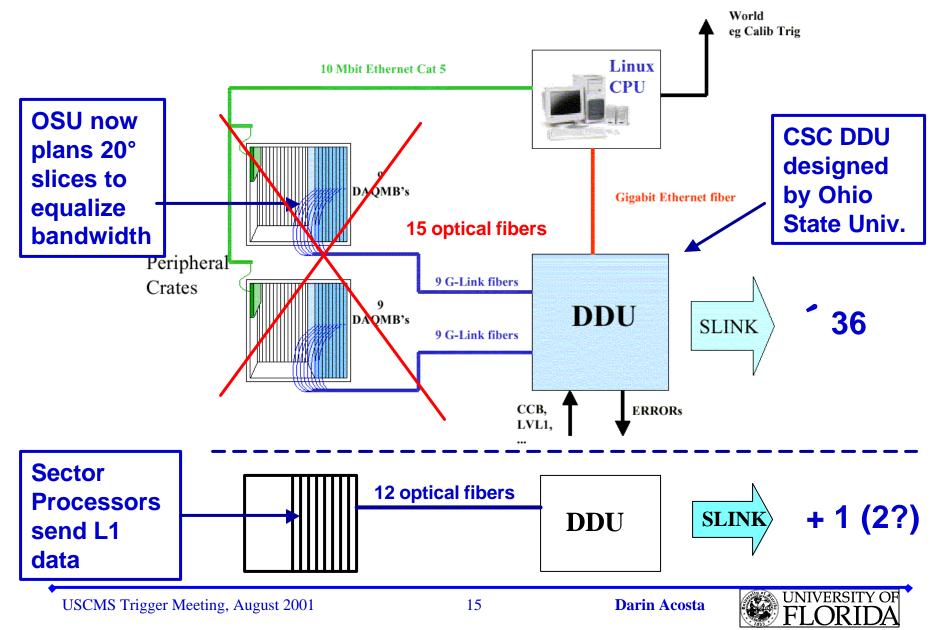

Send input of SR and output of SP to DAQ stream for diagnostics

Track-Finder DAQ acts as additional DDU for EMU system

- Plan to use existing DDU design by OSU

- **OSU** has decided to use T.I. Chip for serialization

- **12 SP fiber connections fits well into 15 planned for DDU**

- Image: Constant of the second seco

Next step is to have Lev work with OSU (Jason Gilmore) to learn their design

- Check bandwidth and buffer limitations

- Understand how to format our data

- Design buffers and readout on SR/SP

## **Mirror CSC DAQ Path**